情報ガイドステーションメニュー

|

| AMD 3D V-Cacheテクノロジー搭載 |

| 第3世代 AMD EPYCプロセッサーのご紹介 (後半) |

|

前回の記事はこちら → AMD 3D V-Cacheテクノロジー搭載 3世代 AMD EPYCプロセッサーのご紹介 (前半)

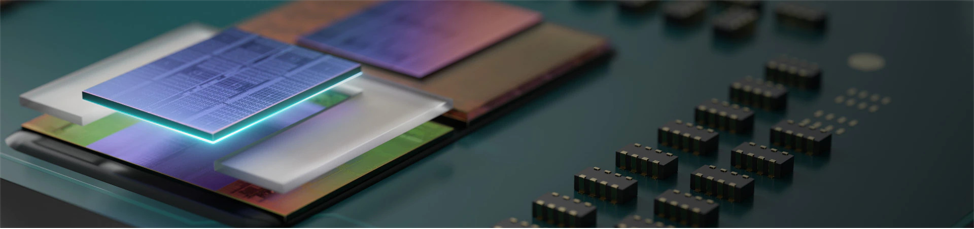

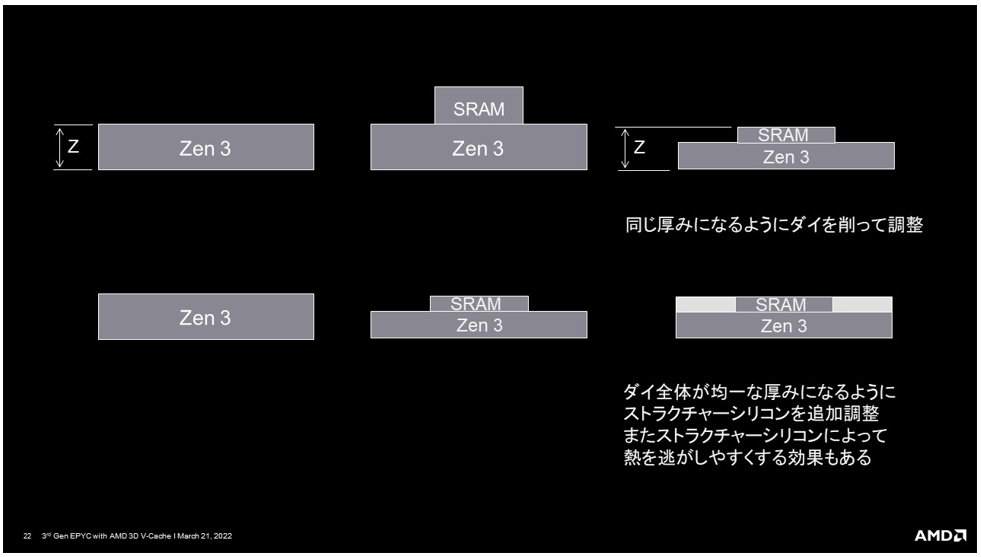

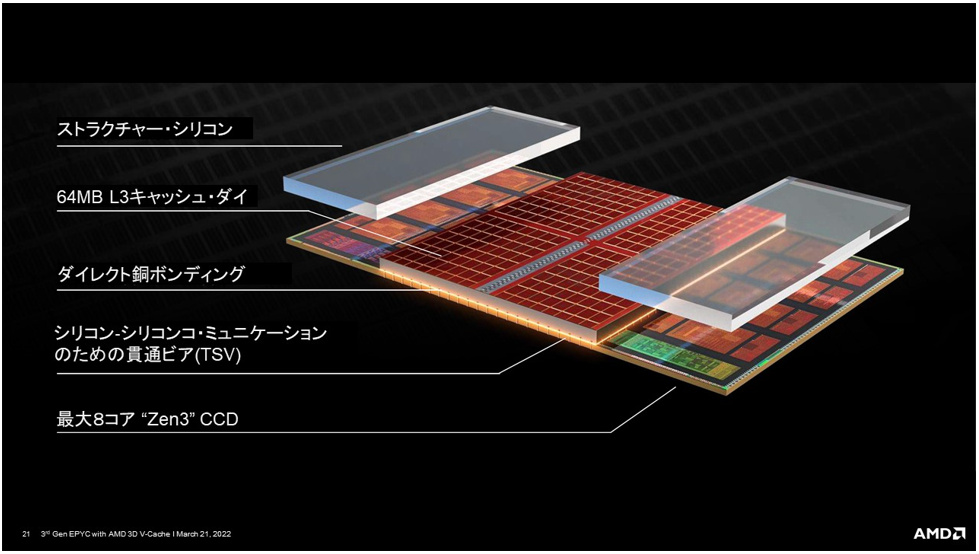

3D実装のデメリットとはいままで多くのメリットやワクワクする技術革新性について説明しましたが、後半はデメリットについて説明します。どんな技術にもデメリットがあり、メリットが大きく上回る技術が生き残ります。もちろん3D V-Cacheにもデメリットがあります。まず、コストが上がることです。キャッシュを増やすために追加されるSRAMのコスト、工程が増えるので製造コストも上昇します。また、2種類のシリコンを重ねるために厚みが厚くなります。他には、熱の問題もあります。2枚のシリコンダイが重なることで発熱を逃がすことが困難になります。 3D V-Cacheでは、このようなメカニカルな問題、熱の問題はどのように解決したのでしょうか? 重なった厚みは削って薄くし、大きさもそろえる。3D V-Cacheテクノロジーは、CPUの上にキャッシュ用のSRAMを張り付けることで大容量L3キャッシュを実現していますが、上にSRAMを重ねているので、その分厚みも厚くなってしまいます。(当たり前ですよね)  この厚み (Z)を、通常のEPYCプロセッサーと同じ厚みになるようにしなければなりません。そのためCPUを削って薄くする必要があります。少し厚くなったとしてもなんとかなるのでは?と思われる方も多いと思いますが、薄い方が熱を逃がしやすく、同じ厚みにすることで既存部品を利用することができます。さらに、次のような秘密が隠されています。EPYCプロセッサーは、最適な熱性能を実現するようにアーキテクチャーとシリコンのフロアプラン(トランジスターの配置)を設計しています。AMD EPYCのCPUは、中央にL3キャッシュが配置(レイアウト)されて、キャッシュを囲むように外側にCPUコアが配置されています。L3キャッシュは演算ユニットの中でも1番発熱の小さい部分になるため、このL3キャッシュの上に重なるようにSRAMを重ねることで、熱密度をコントロールしています。Milan-Xは、熱密度を低く維持し(L3キャッシュを若干超える程度)、CCD上でのオーバーラップを回避しながら、CPUコアデバイス(CCD)上に搭載可能な3D 64MB SRAMセルを設計しています。また、高密度コアやCCDから熱を逃がすストラクチャー・シリコンを搭載することで、3Dチップレット・スタッキングを効率よく熱問題を解決する方法で実現しています。  図10:3D V-Cache 構造 図を見てわかる通りL3キャッシュSRAMとCPUはダイの大きさが異なります。CPUダイと重なるL3キャッシュSRAMの大きさを合わせるためにストラクチャー・シリコンをCPU上部に搭載します。CPUの熱密度が高いところを避けて、SRAMを実装し、熱密度が高いところにはストラクチャー・シリコンによって熱を逃がしやすくなるように設計しました。 AMD EPYC 3D V-Cache 製品概要3Dチップレット技術によってキャッシュ容量を3倍に増やしたCPUですが、製品種類は多くありません。第3世代EPYCプロセッサーでは4つの製品が出荷開始となりました。 TDPは、240W、または280Wで、同TDPの製品と比較すると周波数が若干低くなります。これは、搭載されるSRAMも電力を消費することや、冷却の問題などから周波数がトレードオフの関係にあります。 DELL PowerEdgeサーバーでは、第3世代EPYCプロセッサーをサポートしているR7525、R7515、R6525、R6515、さらにC6525でMilan-Xをサポートします。 詳しくは、こちらの記事を参照ください「国内市場シェアNo.1および満足度1位に関するお礼と、PowerEdge最新情報」 AMD EPYC 3D V-Cache 製品一覧(表1)

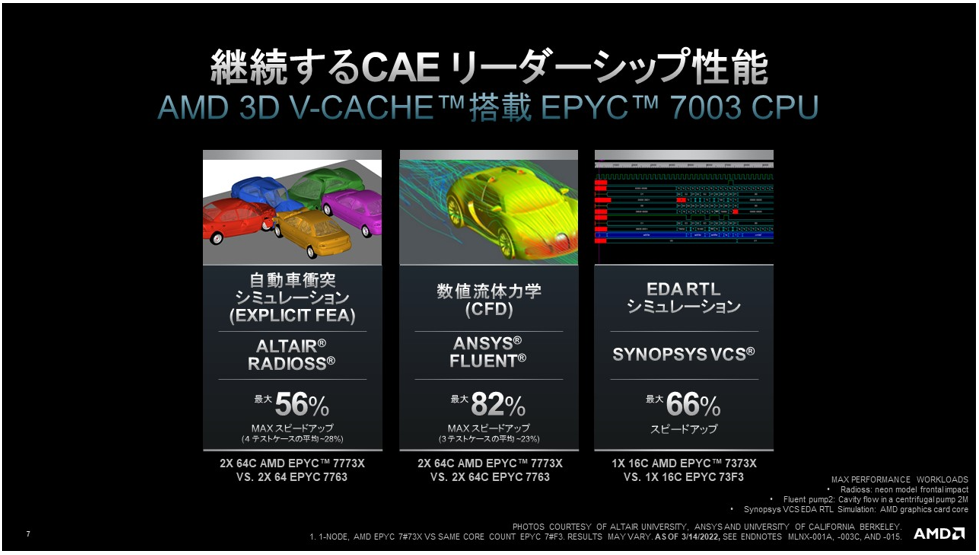

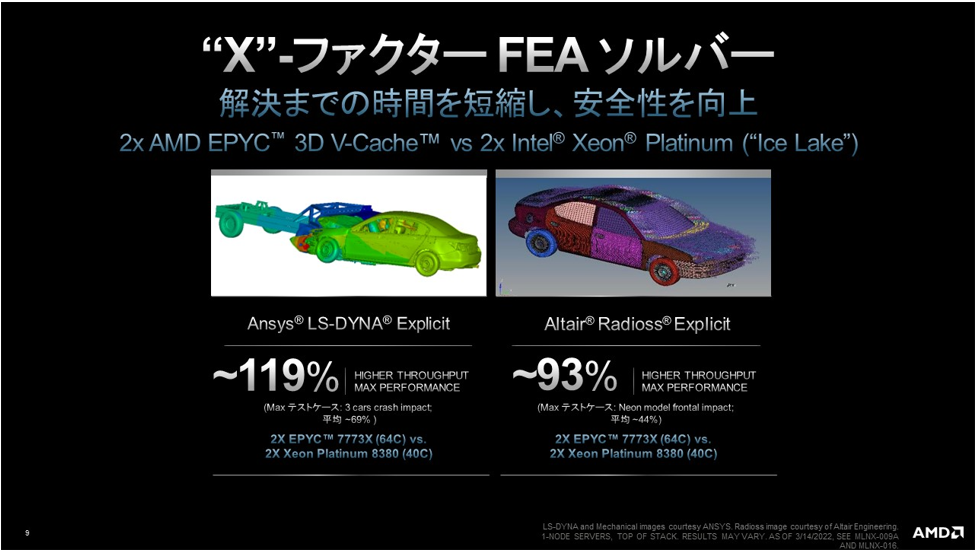

ベンチマーク結果3D V-Cacheテクノロジーは、その名の通りキャッシュを増やすテクノロジーです。搭載されているシリコンはSRAMなので、富岳で採用されているような超高速なメインメモリとして利用することも可能でしたが、AMDはキャッシュとしての実装を選択しました。また一般的にCPUはSRAMを増やすとキャッシュのアクセス・レイテンシーが増えてしまいますが、3D V-Cacheでは、そのレイテンシーを小さく実現できるように設計しました。 HPC分野、特に製造業で利用が高い数値流体力学(CFD)や有限要素法解析(FEA)。半導体設計で利用されるRTLシミュレーションでのベンチマーク結果を以下に示します。    これらのアプリケーションでは、キャッシュのサイズ(容量)が増えたことによって、コードのローカリティが上がり性能が向上したと考えられます。 関係する参考URLを以下にリストアップいたします。 ◢ Synopsys社のブログ https://blogs.synopsys.com/from-silicon-to-software/2022/03/21/eda-workloads-amd-processors/ ◢ Cadence社の動画 Delivering Breakthrough EDA Performance to Boost Engineering Productivity – YouTube ◢ Siemens社のYouTube動画 Boosting Performance for Critical EDA Applications – YouTube 今後の計画CPUコア上の3Dキャッシュスタッキングは、AMDの3Dパッケージの導入段階に過ぎません。3Dキャッシュスタッキングの未来は、IP-on-IPスタッキング、マクロオンマクロ・スタッキング、IPフォールディング/スプリット、および回路レベルのスライシングなど、アーキテクチャーの革新を数多く生み出すでしょう。いまは、AMDが先行していますが、すぐに競合他社も追いついてくると予想しています。 ついに完成した夢の技術を搭載したCPUをぜひお試し下さい。 最後まで読んでくださりありがとうございました。 日本AMD株式会社 ソリューション・アーキテクト 中村正澄

|