情報ガイドステーションメニュー

|

| AMD 3D V-Cacheテクノロジー搭載 |

| 第3世代 AMD EPYCプロセッサーのご紹介 (前半) |

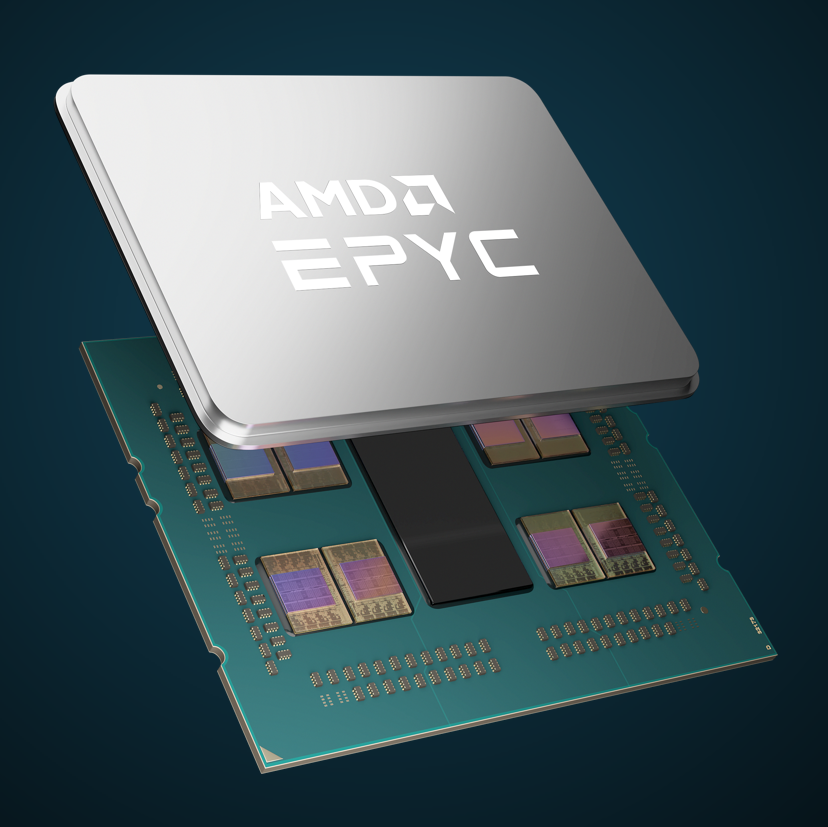

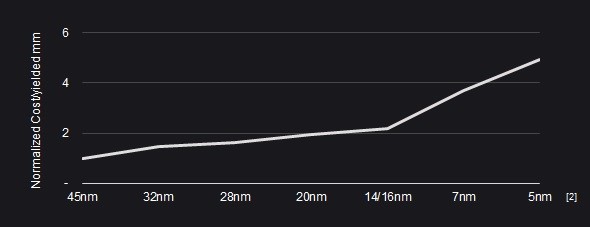

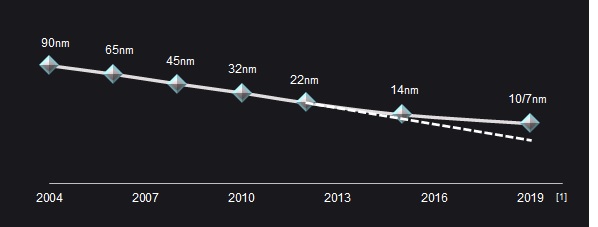

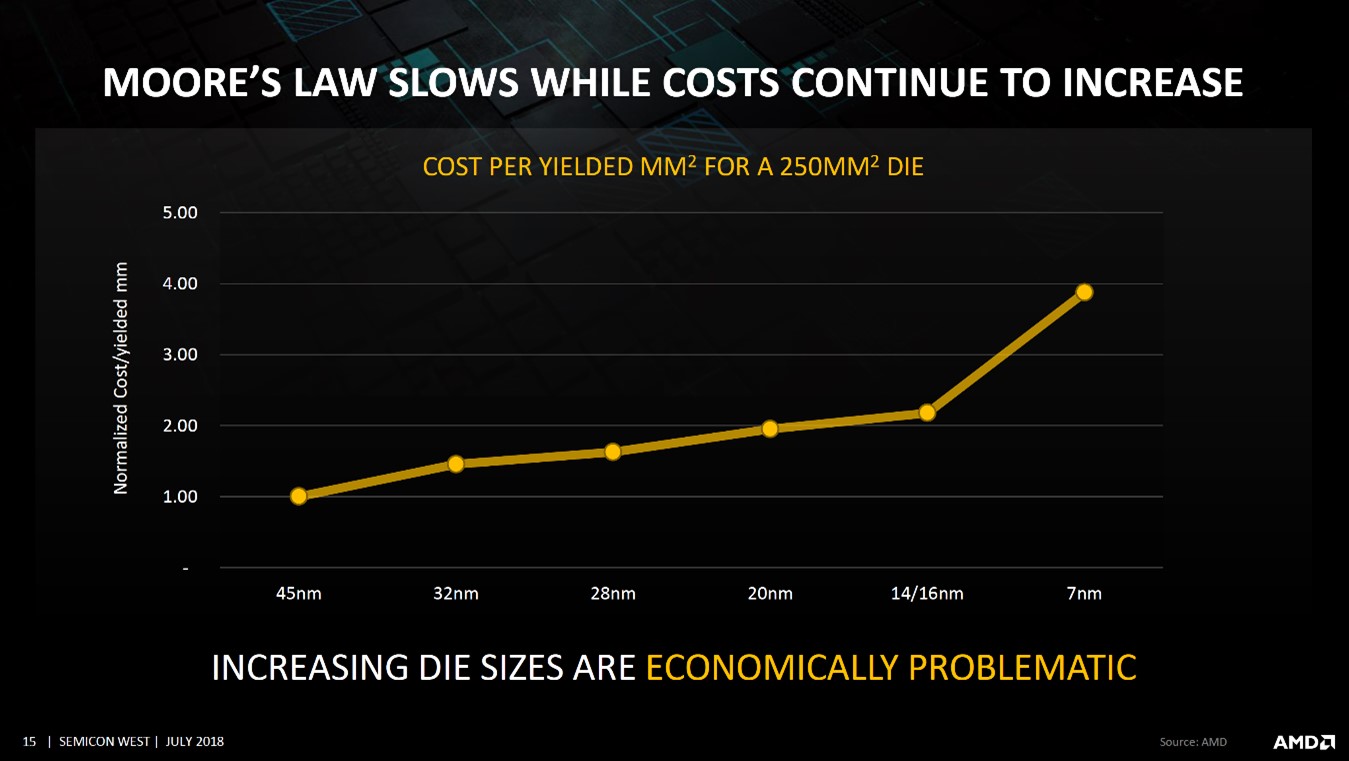

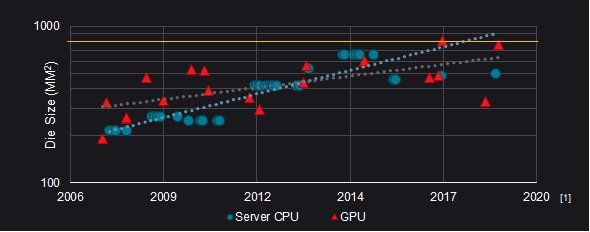

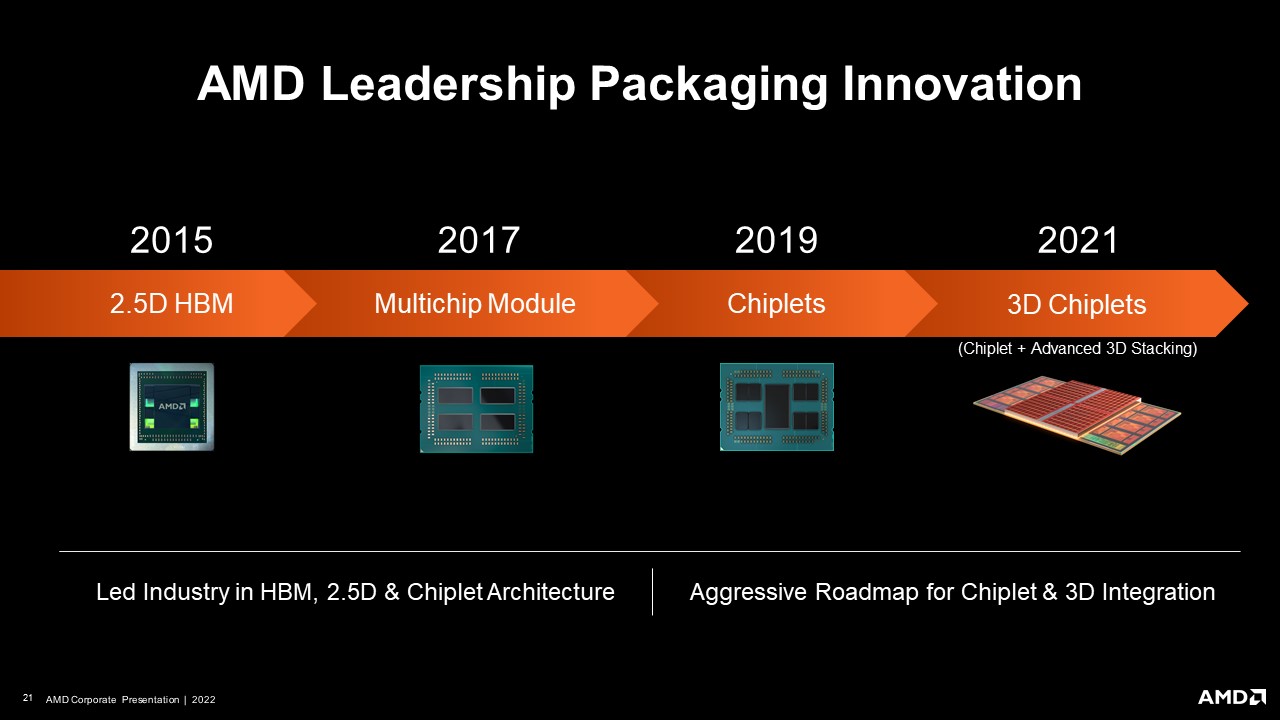

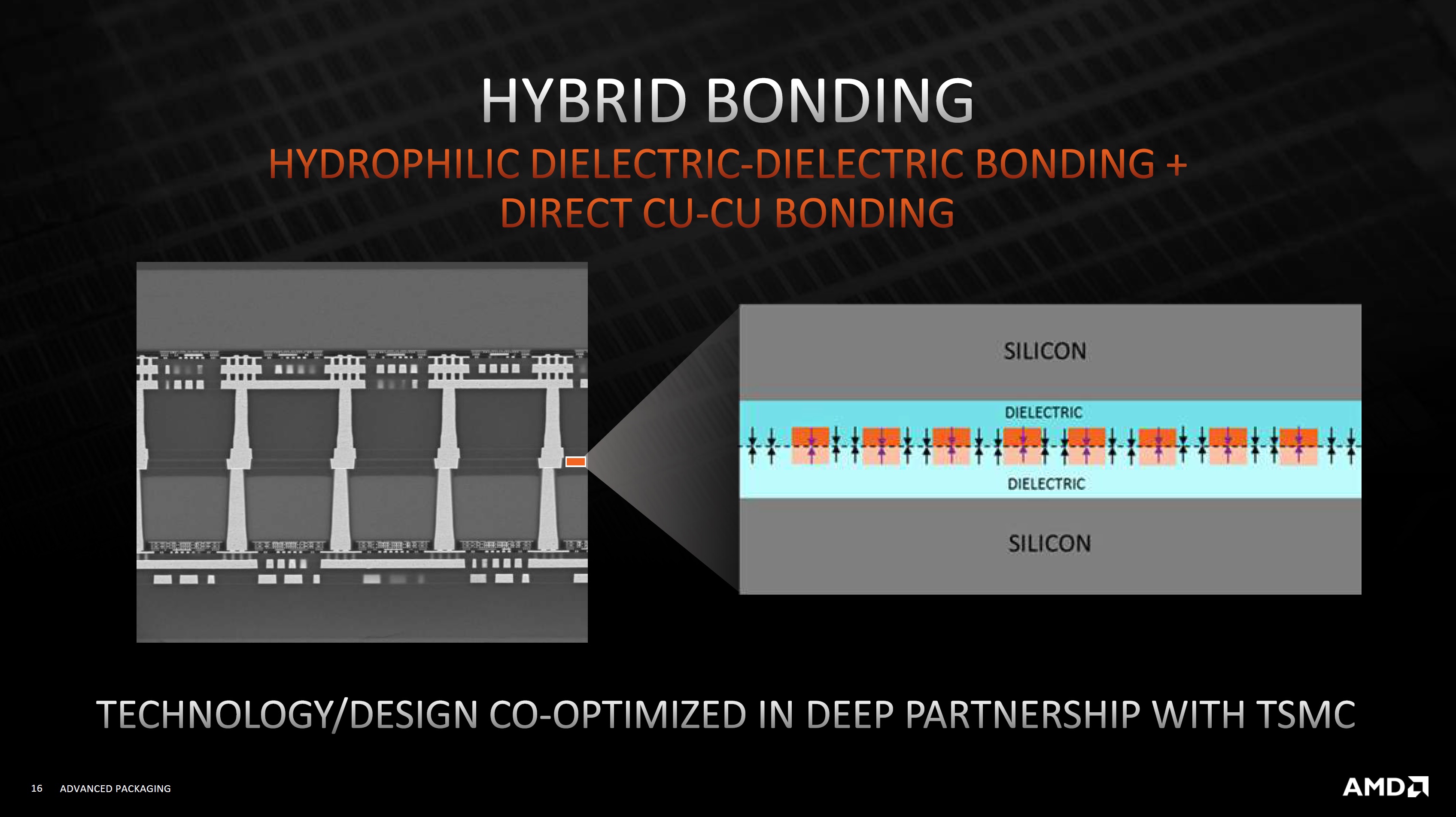

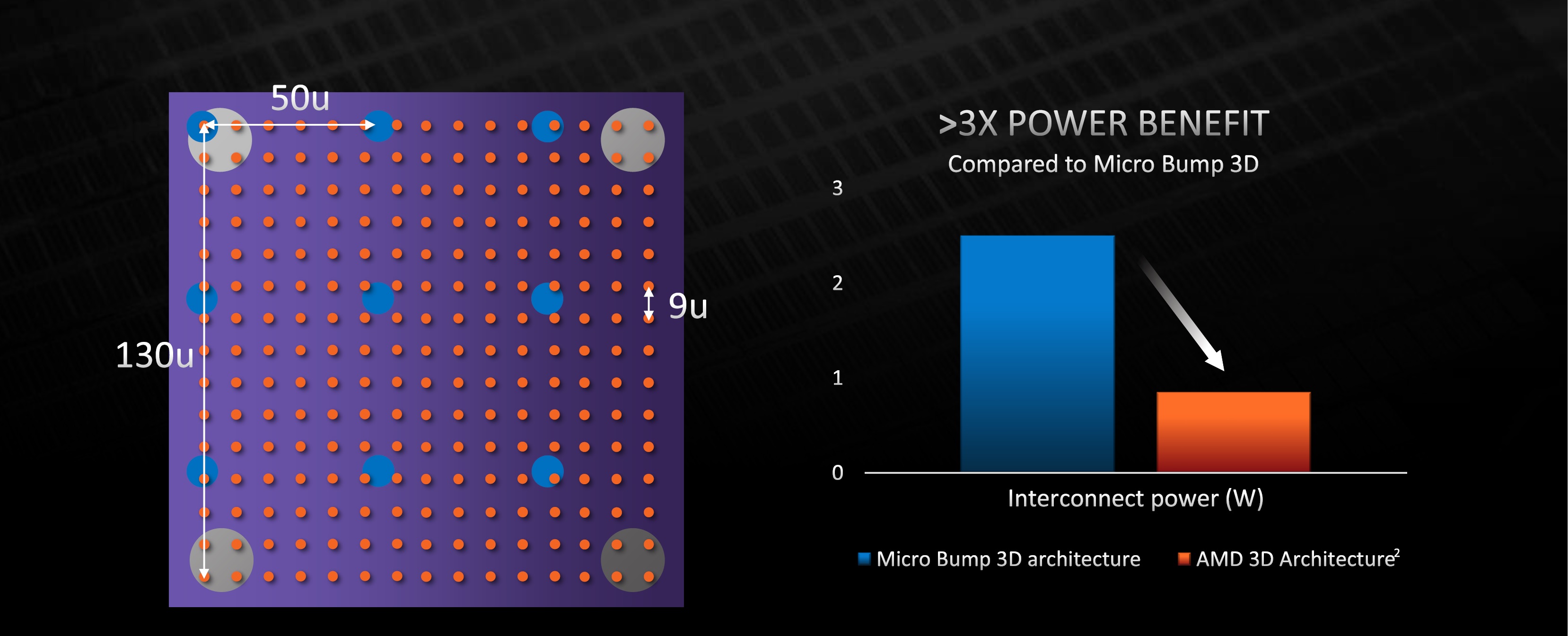

はじめに本BLOGの執筆はAMDのエンジニアが書いています。今回は、普段とは毛色の違う内容をお届けしたいと思います。通常は目にすることのない、しかし重要なパーツであるCPUについて深く堀りさげた内容をお届けしたいと思います。  CPUテクノロジートレンド ムーアの法則の限界 いま、CPU業界は技術的な転換期にあり、その結果、競争が激しくなり、熱いことになっております。いままで半導体はムーアの法則という1つの指標に沿って発展を続けてきました。インテルの創業者のひとりゴードン・ムーア博士が1965年に発表した論文で半導体のトランジスターの集積度が、約2年間で2倍になるという法則です。発表当時は、10年は続くだろうという予測でしたが、驚くことに2010年代後半まで継続しました。半導体メーカーだけでなく、製造装置ベンダーや材料などのサプライヤーもこの指針に沿うように努力を続けてきた結果だと思います。 しかし、2010年ごろからこのムーアの法則が鈍化しだしてきました。2次元方向だけで集積度を高めていくという従来の方法では、ムーアの法則を継続することは困難になってきました。当時Fabレスに進化を遂げたAMDは、いち早く対策に取り組みました。皮肉なことに自社工場を手放したことから、半導体微細化加工のテクノロジー進歩の問題にいち早く取り組むことができたのです。  図1:ムーアの法則の減速 出展:AMD 2020 VLSI short course : presentation by Sam Naffzier SVP and Fellow 製造コストの課題そして、追い打ちをかけるかのように14nmのプロセスを超えたあたりから製造コストの増加が顕在化してきました。半導体の利点の1つに、大量生産が可能で、そのため製造コストが下げられることにあります。しかし、14nmを超えたあたりから露光装置、またそれに付随する技術の導入のために必要な初期投資が大きくなり、それにより製造コストが大きく跳ね上がりました。 また、半導体にはレチクル・リミット(Reticle limit)と呼ばれる半導体のダイサイズの大きさの限界があります。これはレンズの開口数の限界からくる製造できるダイサイズ(大きさ)の限界です。現在は800mmのサイズのあたりが限界で、もう20年近く変化がありません。2000年のころから、すでに最大サイズの限界ぎりぎりの大きさのCPUやGPU を製造することができました。しかし、これ以上大きなサイズのチップを製造することは難しい状況が続いています。また、これらの大きなチップは非常に歩留まり(イールド)が悪く、コストが高く、大量生産できないという問題を抱えています。話をもとに戻します。最新テクノロジーで生産されるCPUは、同サイズでも製造コストが高く、大きなサイズの歩留まりはより厳しく、コストが跳ね上がるという状況にあります。  図2:250 mm2 サイズのチップ(ダイ)の製造コスト/歩留まり 出展:AMD 2018 SEMICON WEST : presentation by Sam Naffzier SVP and Fellow  図3 :レチクル限界Reticle Limit 出展:AMD 2018 SEMICON WEST : presentation by Sam Naffzier SVP and Fellow AMD パッケージ技術ロードマップこれらの課題にAMDはいち早く取り組みました。まず、AMDが取り組んだのはMCM、チップレットによる製品の開発です。本BLOGでは最新の3Dチップレットに焦点を当てていますので、MCM、CHIPLET(チップレット)の特徴やメリットは、すでに他の方が記事化されているので、ご興味がある方は参考URL先を参照ください。 https://biz.amd-heroes.jp/solutions/265 https://news.mynavi.jp/techplus/article/20180427-623497/ https://pc.watch.impress.co.jp/docs/column/kaigai/1108259.html https://pc.watch.impress.co.jp/docs/news/1392928.html AMDのパッケージング技術への投資と革新は、長期にわたり忍耐強く開発してきたものです。簡単にすぐに完成したものではありません。AMDは、GPUも設計していたことからHBMを利用したメモリとGPUを1つのパッケージに統合したGPUを2015年に量産出荷しています。2017年に初めてMCMによるサーバー製品向けCPU、EPYCプロセッサーの出荷を開始しました。このMCMやCHIPLETの流れは競合であるIntelも同様で、次期サーバー向けCPUからMCMを導入してくると発表されています。  図4:出展:AMD Corp スライド 2022 April 3D CHIPLET技術の登場他社がこれから2.5Dの製品を投入してくるという中、AMDは2021年11月にCEOのLisa Suが「3D チップレット」技術を発表しました。いち早く3D実装による初のCPUを発表し注目を集めました。 実は3D実装技術にはいろいろな種類があるのをご存じでしょうか?3D実装技術はAMDだけが取り組んでいる技術ではありません。IntelのFoveros、SONYやTSMCのWoW、micro Bump 3Dなどなど、いろいろな技術があり、それぞれ特徴、特性があります。重要なのは、作りたい製品に合った最適な技術を選択することです。 AMDが製品化した3D V-Cacheテクノロジーは、ハイブリッドボンディングとシリコン貫通ビア(TSV)を組み合わせた技術です。3D V-Cacheテクノロジーは、CPUの上にSRAMを重ねることでキャッシュの容量を大幅に増やす技術です。一言で表現すると、CPUのキャッシュを得盛りにする技術です。3D V-Cacheは、先端的なパッケージング技術で、この技術を適用したMilan-Xが、初のCPUで3次元実装が使われた半導体製品となります。 3次元実装って、なにがすごいの?都会の住宅が、一戸建ての住宅から高層マンションに変わったように、CPUも平屋から高層マンション化することで限られた敷地に多くの人が住むことができます。同様にCPUも3D化することで面積当たりの集積度を上げる事が可能になります。具体的なアプリケーション性能など、大容量キャッシュを実現した3D V-Cache搭載CPUのメリットはBLOGの後半で説明します。 3次元実装って、どうやって実現したの?AMDの3Dチップレット・テクノロジーは、TSMC社と共同開発し、TSMC社の「3D Fabric」技術を活用したハイブリッド接合およびシリコン貫通ビア(TSV)を組み合わせた新しいプロセスによって実現しています。TSVは、AMD 2Dチップレットの200倍以上の相互接続密度を備え、既存のインテル3Dスタッキングソリューションと比較して15倍以上の密度を備えています。これにより、AMDのIPブロックをより効率的かつ高密度に統合できるようになります。ダイ間インターフェイスは、はんだバンプ等を一切使用せず銅対銅結合を直接使用します。(ここがすごいのです。)  図5:ハイブリッドボンディング 出展AMD Hotchips 2021 Sr. Fellow Raja Swaminathan このアプローチによって、他の3次元アプローチよりトランジスター密度と相互接続ピッチが大幅に向上します。これは現時点で最も柔軟性の高いアクティブ・オン・アクティブ・シリコン・スタッキング技術と言えます。これらの小型シリコン貫通電極および直接銅対銅接続により、競合するマイクロバンプ3Dアプローチの信号あたりの消費電力の3分の1未満で、SRAM/CCD帯域幅2TB/秒を実現することができるのです。AMDの3Dチップレットアーキテクチャーは、銅対銅の直接ハイブリッド接合技術と、ダイ間通信用のTSVを使用し、シリコンの最小領域で最高の帯域幅を実現するよう綿密に設計されているのです。  図6:C4バンプ、マイクロバンプ、TSVのピッチの違い(実際のスケールとは異なります。) 出展AMD Hotchips 2021 Sr. Fellow Raja Swaminathan 他のプロセッサーメーカーが使用している、はんだベースのマイクロバンプ技術と垂直式TSVは、従来のはんだベースのパッケージング技術に基づいており、ピッチを50uから36uまで向上することに成功しています。しかし、まだ不十分です。AMDの3Dチップレットアーキテクチャーははんだを用いず、バックエンドデザインのルールベースのTSVを用いたシリコン製造方法を使用するので、9μmピッチでTSVを接続できるのです。これにより究極の帯域幅アーキテクチャーが可能となります。  図7:マイクロバンプと比較した消費電力とダイ面積のメリット 出展AMD Hotchips 2021 Sr. Fellow Raja Swaminathan もう少し分かりやすく説明するとCPUとその上に張り付けられるSRAMの間を非常に細かい配線で接続しているのです。多くのベンダーはマイクロバンプを利用してはんだで接続していますが、3D V-Cacheははんだを使わずに接続(実現)しているところがすごいのです。 このような技術向上により、相互接続のエネルギー効率が3倍以上に向上し、相互接続密度が15倍以上になり、競合他社のマイクロバンプ3Dアーキテクチャーと比較して信号性能と電力性能も向上しています。 かなり細かい話になってしまいました。最後まで読んでくださってありがとうございます。最後に3D V-Cacheを解説する、日本語字幕付きのAMDのYouTubeもご紹介したいと思います。  図8:AMD Youtube AMDHEROSJP チャンネル https://www.youtube.com/watch?v=RcP8zYB0a04 よろしければ「いいね」とチャンネル登録もお願いします! BLOG後半は、ベンチマーク結果や3次元実装のデメリットなどについて解説したいと思います。お楽しみに! 日本AMD株式会社 ソリューション・アーキテクト 中村正澄 次の記事はこちら → AMD 3D V-Cacheテクノロジー搭載 第3世代 AMD EPYCプロセッサーのご紹介 (後半)

|